数字电压表设计教程之LTC2308数据手册解读

1前言

LTC2308 是亚德诺半导体公司( Analog Devices Inc,ADI) 的一款低噪声、12 位高精度、逐次逼近型、 8 通道、采样率高达 500 kSPS (ADC输入信号最高不能超过500KHz,按照Nyquist采样定理则建议输入信号在250KHz以下)、SPI输入时钟最高可达40M、支持串行外设接口( Serial Peripheral Interface,SPI)的模数转换芯片 。

2LTC2308的功能框图及引脚定义

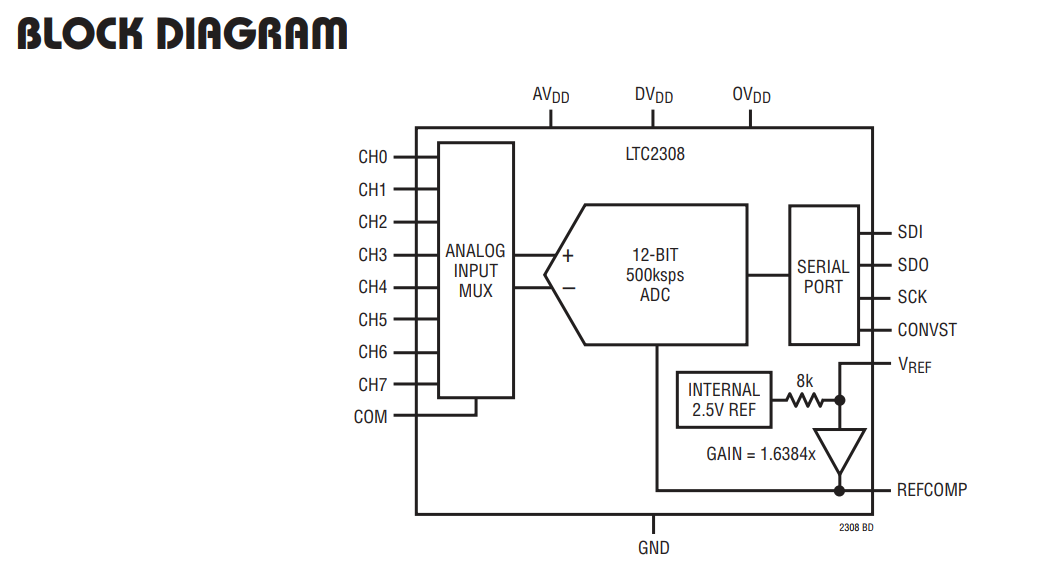

LTC2308的功能框图:

引脚定义(来源参考 LTC2308 datasheet LTC2308fb.pdf 的第7页):

3LTC2308的工作模式设置

LTC2308的8个模拟通道能配置成为单端、差分式通道,以及单极性、双极性通道,通过四线式 SPI与其他数字接口电路相连。

当为单端输入时,每个通道相对于COM端,单极性状态下可以输入0~4.096V的范围,双极性为±2.048V的范围,其中,负数是以2的补码形式表示。当为差分模式输入时,CH0与CH1、CH2与CH3、CH4与CH5、CH6与CH7可以分别构成差分对信号,能同时对差分信号进行采样以减小共模干扰。当输入源的阻抗较大时,需要的获取信号时间也会相应增多。

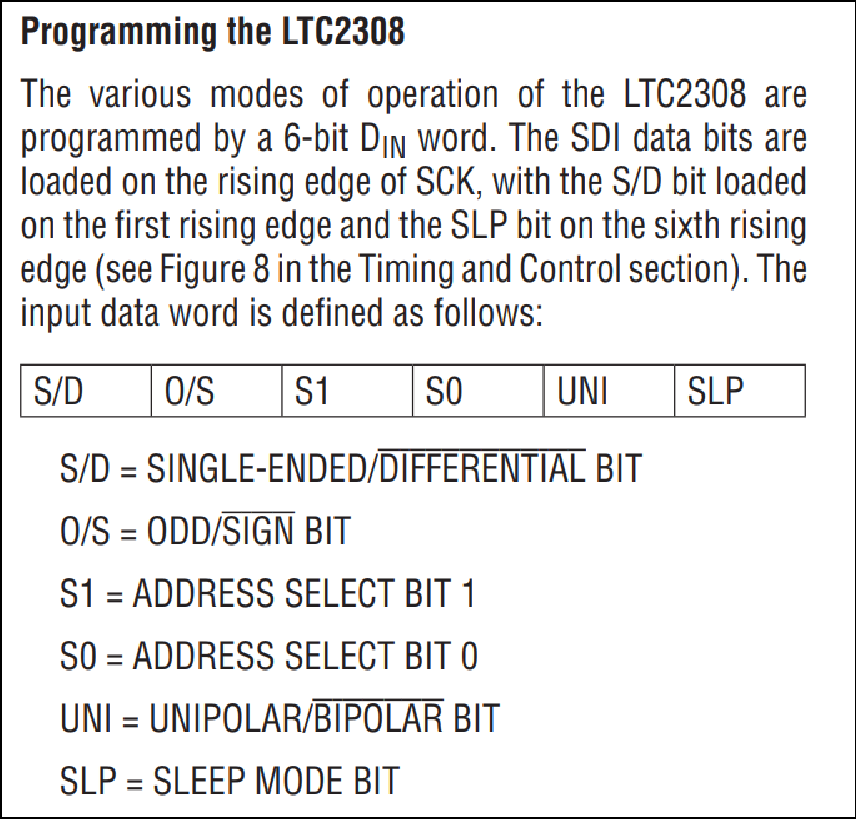

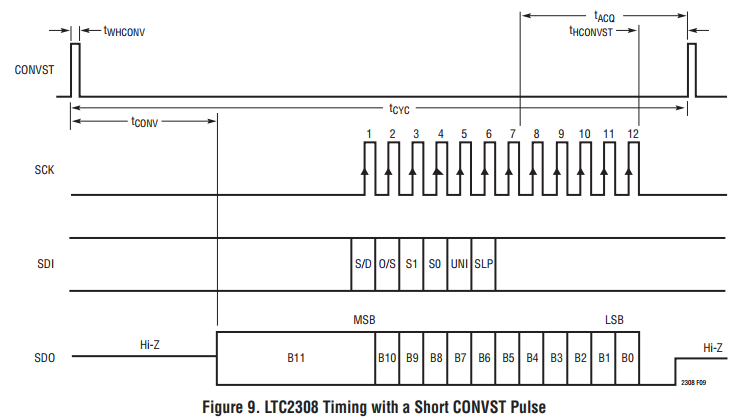

LTC2308的各种工作模式是可通过6位DIN字可编程设定的。(参考下文时序图,来自LTC2308 datasheet LTC2308fb.pdf 的第10页)。

6位DIN字定义如下:

LTC控制数据为6位,由高到低依次为:S/D、O/S、S1、S0、UNI、SLP。

S/D控制芯片是单端还是双端差分式模式。

O/S在差分方式下,控制两个信号的正负极性,当O/S为1时,表示奇数通道输入信号的符号为正,偶数通道输入信号的符号为负;当O/S为0时,表示奇数通道输入信号的符号为负,偶数通道输入信号的符号为正。O/S在单端模式下,当O/S为1时,表示奇数通道输入信号的符号为正;当O/S为0时,表示偶数通道输入信号的符号为正。

在双端模式下,S1、S0构成2位通道选择信号,正好可以选择4组差分通道。在单端模式下,S1、S0构成2位通道选择信号,用于选择奇数通道里的4个通道以及偶数通道里的4个通道。

UNI为极性控制信号,其为1时,输出单极性信号,为0时,输出补码形式的双极性信号。

SLP则是控制芯片是进入 SLEEP 还是 NAP 状态。

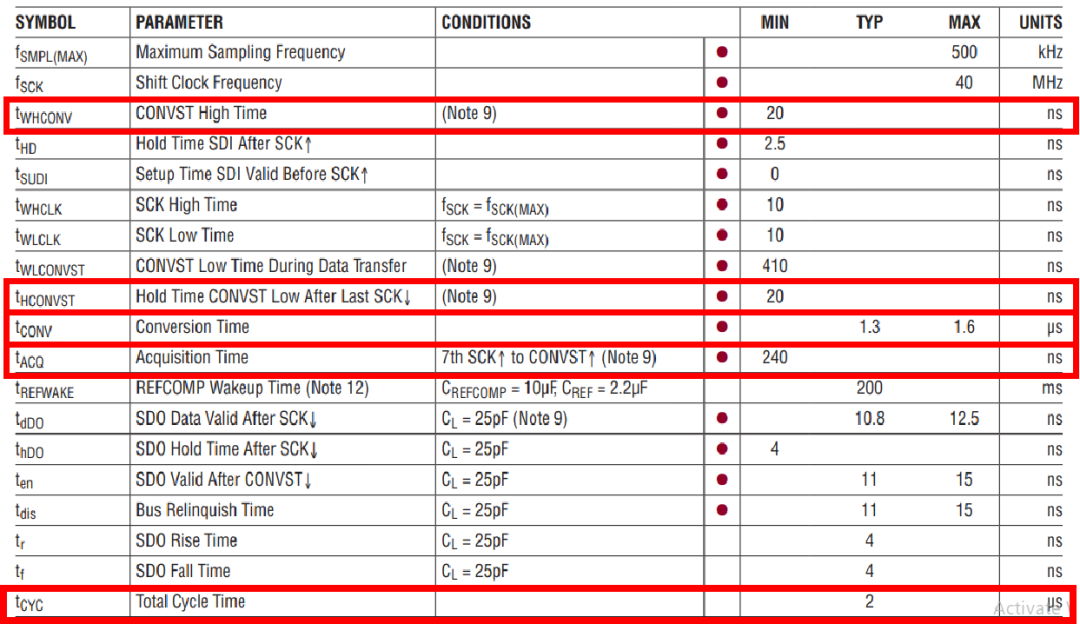

在传输完第6位控制字之后,芯片还需要至少 240 ns的 tACQ的获取时间之后才能再次将 CONVST拉高来启动下一次转换。

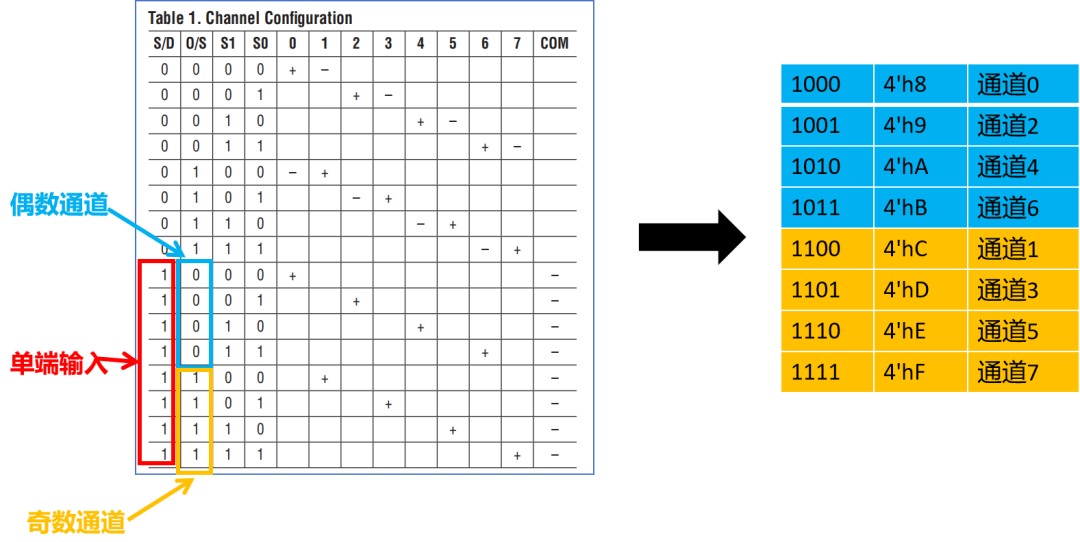

继续参考参考LTC2308 datasheet LTC2308fb.pdf 的第10页的Table1可得到本案例通道选择的配置字:

4LTC2308的功能框图及引脚定义

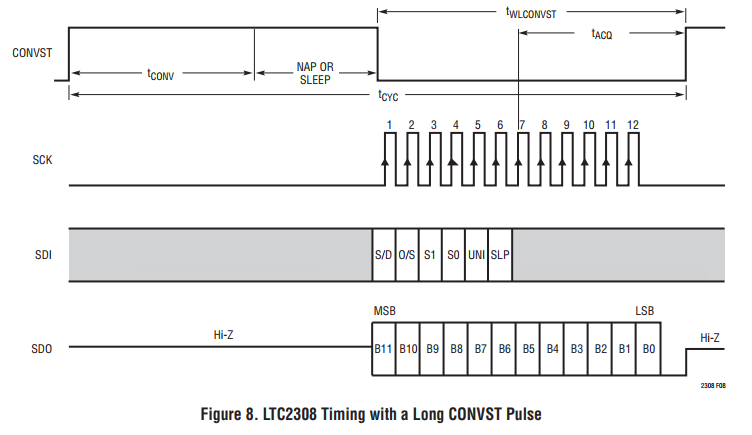

参考LTC2308fb.pdf第17页, 该器件SPI协议时序图有两个。

第一个:

在第一个时序中,当转换完成后,CONVST仍保持高电平时,芯片会根据SLP位设置的逻辑电平进入NAP(SLP=0)或SLEEP(SLP=1)模式。当CONVST返回低电平时,LTC2308从SLEEP模式释放,需要200ms才能唤醒并为VREF引脚上的2.2uF电容和REFCOMP引脚上的10uF电容充电。

第二个:

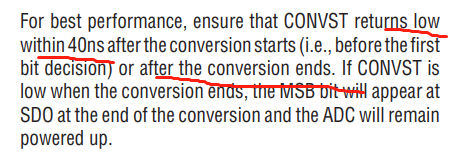

DE10-Standard 的SystemCDDemonstrationsFPGAADC 这个案例里面我们使用的是第二个时序图,原因是为了LTC2308 表现的性能更好,尽量选择:

1. 在转换开始之后的40ns内返回低电平

2. 在转换结束之后返回低电平

关于这个的描述请参考LTC2308fb.pdf第14页:

所以实验里面选择第二个时序图。

第二个时序图中的各个时间定义(参考LTC2308fb.pdf的第5页):

把上面的表格摘出并翻译如下:

第二个时序图显示了在转换时间结束前,CONVST信号回到低电平。在此模式下,ADC和所有内部电路保持通电状态。当转换完成后,SDO的输出数据序列的MSB将在数据总线被启用后有效。在CONVST上升沿后1.3μs之后,随着脉冲SCK的节奏,SDO将从LTC2308中输出数据,SDI则将配置数据加载到LTC2308中。第一个SCK上升沿将S/D位加载到LTC2308中,第六个SCK上升沿将SLP 位加载到LTC2308中。SDO在每个SCK脉冲的下降沿输出数据。

送出convert trigger后,经过tCONV时间后才能送出SPI clock, 通过SDO 接收ADC结果,并同时通过SDI 设定下次convert的模式。SPI clock结束后,至少要等tHCONVST时间,才能送出下一个convert trigger。LTC2308设计为在控制字发送后开始采集(控制字发送在第6个时钟完成, 第7个时钟就可以开始采集了),以适配不同模式下的时序要求。

- 海南澄迈集中签约173个项目 意向签约金额约673.6亿元,海南澄迈集中签约173个项目 意向签约金额约673.6亿元

- 台积电三季度利润新高:多终端高成长,先进工艺涨价进行时

- 行走江河看中国丨从安澜梦到天鹅城,三门峡的人与自然共舞新篇,行走江河看中国丨从安澜梦到天鹅城,三门峡的人与自然共舞新篇

- TOPPS与阿里鱼、天猫正式达成战略合作,中国首家官方旗舰店入驻天猫

- 新疆阿拉尔市重盐碱地“沙漠水稻”首年平均亩产超600公斤,新疆阿拉尔市重盐碱地“沙漠水稻”首年平均亩产超600公斤

- 均普智能拟募资不超过11.61亿元用于项目建设

- 海南自贸港“三大吸引力”揽外商,海南自贸港“三大吸引力”揽外商

- HT4822立体声耳机放大器:音频设备的概述

- 深度数智将携最新 RISC-V + AI 创新产品 亮相10月多场RISC-V及开源峰会!

- 报告:商业健康险要完成从“边缘补充者”到“生态协同者”的转变,需聚焦三大方向

- 从拉赫马拉松到马勒宇宙,未来两月都在东方艺术中心

- 美国前总统拜登正接受癌症放射治疗

- 发生了什么?“牛市旗手”突然大涨

- 深圳技术大学:超薄石墨烯应变传感器阵列,用于毫米级分辨率的高灵敏度多功能传感

- 电力监控系统如何在智能变电站使用?

- 倾佳电子B3M010C075Z碳化硅MOSFET深度分析:性能基准与战略应用